MIPI I3C & Debug Over I3C Plugfest

Taipei, Taiwan

9-10 September 2024

MIPI I3C/I3C Basic Testing Details

Platform: Standardized cabling (.1 inch spacing – female-female wires, GND, SDA, GND, SCL, GND). Legacy I2C device allowed. Power supply may be needed for targets. 1.8v and 3.3v devices present.

Features under Test:

- Pure and Legacy I3C SDR Read/Write

- I3C SDR Read/Write

- Dynamic Address Assignment (including SETDASA and RSTDAA)

- IBI with/without MDB – if supported

- Basic Direct CCC’s

- Enter/Exit HDR (for SDR only devices)

- DDR Read/Write/CRC – if supported

- TSP Read/Write – if Target supported

- Controller/Target Error Handling

- Multi-Target Topologies (at least two I3C devices) – After confirmed point-to-point functionality

- Include Direct/Broadcast CCC’s

- HCI v1.0 related tests – to ensure a hardware and standard software compatibility

- Timing Control

- Sync Mode

- Async Mode 0/1 and Async Mode Exit

- Secondary Controller/Main Controller Handoff – if supported

- Target Reset

- Multilane features

- 1.2V support for devices that are supporting it

- Group Addressing

- Any other I3C v1.1.1 and I3C Basic v1.1.1 capabilities supported

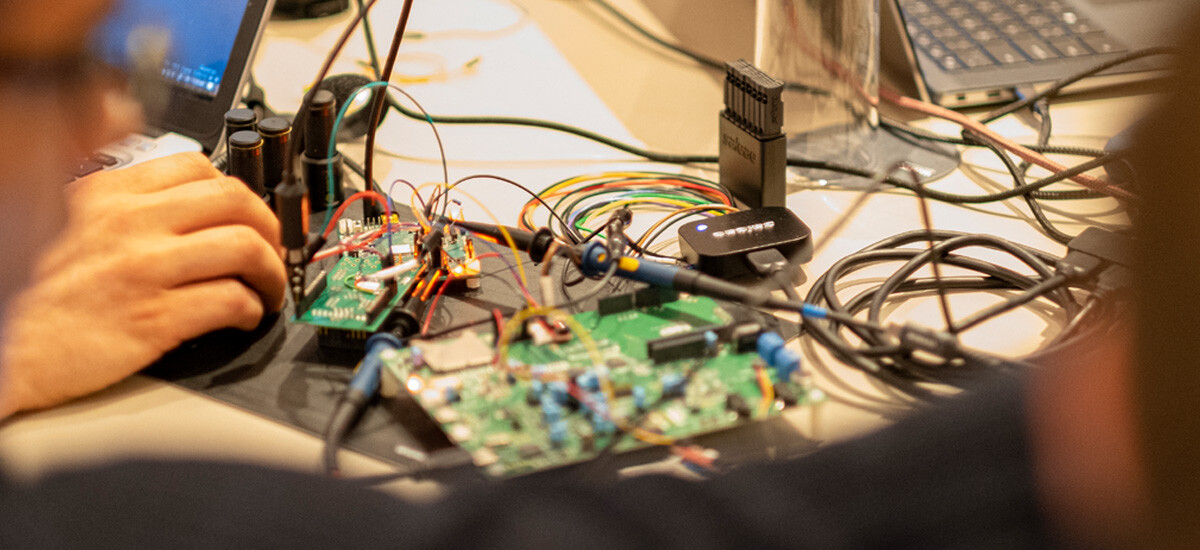

Test Equipment: Test companies may bring oscilloscopes with I3C protocol Trigger and Decode analysis and active probes

Anticipated Test Matrix: Approximately n Controllers X m Targets

Other: Device Characteristics Register (DCR) assignments are available for each I3C Target

I3C Physical Interface

- Objective: Maintain a consistent physical interconnect of design and length for easy interoperation between varied test PCBs and typical I3C functionality

- Design: 0.1 inch spacing female to female AWG 26 ribbon cable with solderless individual connectors.

- Pinout: GND, SDA, GND, SCL, GND

- Length: Max 15cm (0.02Ohm, 2.5pf)

- Example: https://www.amazon.com/dp/B01L5ULRUA?psc=1

I3C Conformance Test Suite for I3C/I3C Basic v1.1.1

A conformance test suite (CTS) has been developed to improve the interoperability of products that adopt the MIPI I3C interface. It defines a set of conformance or interoperability tests whereby products can be tested against other implementations of the I3C or I3C Basic v1.1.1 specifications. The latest version of the CTS focuses on SDR-only devices without optional I3C capabilities, all controller and target error detection and recovery methods, and basic HDR Enter/Tolerance/Restart/Exit in scope, with HDR-DDR under consideration.

MIPI Debug Over I3C Testing Details

The MIPI Debug Working Group will also host a plugfest concentrating on checking the interoperability of their devices against the foundational requirements of Debug Over I3C v1.0 to ensure features such as the debug-specific common command codes (CCCs) and in-band interrupts (IBIs) are working.

Participants would be asked to bring one or more of the following devices for testing:

- Debug and Test System (DTS), also referred to as the I3C Controller

- Test System (TS), also referred to as the I3C Target, and/or

- Protocol Analyzer

Minimum Requirements:

- Dynamic Address support with ENTDAA

- I3C Basic v1.0 support or newer (although full I3C is fine)

- SDR Mode

- Targets:

- Report DCR value 0xC9

- Present at least one Network Adaptor

- Support DBGOPCODE CCC with necessary opcodes (applicable for NA) including SELECT, CFG, START/STOP, etc.

- Support IBI Requests: DBGSTATUS and DBGERROR

- Support Private Write/Read transfers to/from the selected NA

- Work with I3C transfer rate of at least 2 MHz (or better)

- 1.8V support

- Support any header in MIPI Debug & Trace Connector Recommendations white paper.

- The other option would be to use NIDnT multiplexing specifically USB Type-C with SBU pins.

Preferred configuration (what we hope to see):

- I3C Basic v1.1.1 support (although full I3C is fine)

- SDR Mode with any HDR Modes

- Targets:

- Present two Network Adaptors:

- One for control (CMD/RESP) such as SPP and/or SAM

- Include all mandatory registers/commands

- One for trace (STP and/or TWP)

- Support DBGOPCODE CCC with all opcodes, including thresholds

- Support IBI Requests: all types (including DBGDATAREADY)

- Work with I3C transfer rate of up to 12.5 MHz (maximum)