MIPI I3C HCI™

MIPI I3C Host Controller Interface

Developed by: Software Working Group

A host controller interface for efficiently accessing MIPI I3C devices and capabilities

Quick Facts

-

Fundamental Features

- Publicly available to developers and the open source community

- Enhances the MIPI I3C and MIPI I3C Basic bus interface for connecting peripheral devices to application processors

- Defines a common set of capabilities for the host controller and the software interface

Get the Specification

-

Current Version

MIPI I3C HCI℠ v1.2 (April 2023)

Member version | Public version

| Public version

-

Related Specifications

-

Previous Versions

MIPI I3C HCI v1.1 (May 2021)

Member version | Request public version

| Request public versionMIPI I3C HCI v1.0 (April 2018)

Member version | Request public version

| Request public version -

Frequently Asked Questions

FAQ v1.0 for I3C HCI v1.2

Member version |

Overview

General Info

-

Overview

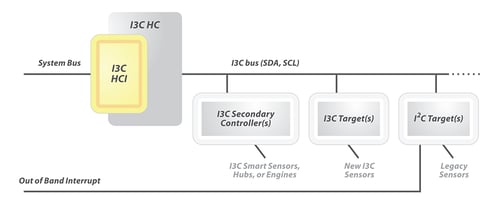

The MIPI I3C Host Controller Interface (MIPI I3C HCI℠) specification defines an interface that operating systems use to access MIPI I3C® devices and capabilities. It delivers crucially needed efficiency for designers of smartphones, computers, Internet of Things (IoT) devices, automotive systems and other applications that leverage the scalable, low-power, medium-speed, two-wire I3C utility and control bus interface.

MIPI I3C and MIPI I3C Basic℠ (the publicly available subset version of the specification) are used for connecting peripherals to application processors. The unifying I3C/I3C Basic bus interface can connect multiple peripheral devices from various vendors to an application processor, streamlining integration and improving cost efficiencies.

With MIPI I3C HCI, application processor vendors benefit from a consistent method for interfacing to MIPI I3C, eliminating the need for product-specific I3C drivers. Instead, operating-system vendors, developers and distributors can offer generic I3C drivers that are portable across hardware platforms, helping to control cost and complexity, and freeing designers to focus their efforts on developing applications rather than interfaces. This allows vendors and developers to easily and efficiently integrate support for I3C, for applications that go beyond simple sensor devices.

MIPI Alliance welcomes contributions to the specification. If you would like to contribute, please contact the MIPI Software Working Group at software@mipi.org.

-

Using MIPI I3C HCI

MIPI I3C HCI defines a common set of capabilities for the host controller and the software interface, allowing for the building of class definitions based on a common set of features. The definition allows for vendor-specific extensions and optimizations.

The specification defines several optimizations based on typical usage. For example, the combo command feature allows for the efficient one-shot transfer of write and then read transfers on the bus.

Key features of the specification include:

- Support for MIPI I3C primary controller operation on the I3C bus

- Two modes of operation: programmable input/output (PIO) mode, delivering direct data interface support with programmable buffer depths for the transmit/response and data buffer, and direct memory access (DMA) mode, providing interface support for scatter gather transfers for data buffers

- Power-efficient operation of the host controller, which helps maximize battery life in mobile devices

- Support for I3C data rates, including I2C fast mode (up to 400Kbps), I2C fast mode+ (up to 1Mbps), I3C SDR (up to 12.5Mbps) and optional I3C HDR Modes (for faster transfers)

- Support for extended capabilities, including vendor-specific ones, to enable more sophisticated hardware or additional functionality

- Group addressing, which enables multicast-type addresses to be assigned to multiple peripheral devices

- Defining bytes for common command codes (CCCs), extending greater flexibility to create additional CCCs or augment the existing CCCs defined in I3C

- Scatter gather for ring pointer, flow control, PIO/DMA mode indicator, ring full indication and other features for improved performance in DMA mode

MIPI I3C HCI is also included in the MIPI Touch family of specifications, making it possible to use touch commands and multiple data streams to add differentiating touch features to a design. Application processor companies can apply the specification to standardize the HCI method used in their devices.

-

Latest Version

For the latest version, MIPI I3C HCI v1.2, the MIPI Software Working Group added new features to align the specification with optional capabilities delivered in the most recent versions of I3C and I3C Basic.

The new optional I3C HCI features include Scheduled Commands and Secondary Controller, Dead Bus Recovery and new register ALT_QUEUE_SIZE for Alternate Response Queue size in PIO Mode.

Additionally, this specification repurposes bit 28 in the IBI Status Descriptor and Broadcast CCC payload data from the Active Controller on the I3C Bus when the Host Controller is in Standby Controller mode and receives certain Broadcast CCCs. The specification addresses memory partitioning in the case where the Host Controller supports both the DAT and DCT in Device Context memory.

Also, v1.2 introduces functionality for in-band interrupt (IBI) credit counters. This feature is designed to afford the host better control of incoming data payloads and support more efficient automated management and usage of memory per target in a given use case.

Many of the new features are particularly valuable in use cases where there is the potential for multiple controllers on an I3C/I3C Basic bus (e.g., a laptop application, with its high number of sensors and high sensitivity to power usage). In such ways, v1.2 makes I3C/I3C Basic a more relevant specification for applications beyond the mobile handsets for which it was initially conceived.

Finally, normative definitions for handling of transfer command and response were removed from I3C HCI in its latest version, given the 2022 release of the separate MIPI I3C Transfer Command Response Interface (MIPI I3C TCRI℠) specification.

-

Diagrams & Tables

Industries